ICSICT2016 Oct. 25-28 2016

S05-6 Analog Circuits I 15:00 - 15:15 PM Oct.26, 2016

## Simple Reference Current Source Insensitive to Power Supply Voltage Variation -Improved Minoru Nagata Current Source -

#### Mayu Hirano,

Nobukazu Tukiji, Haruo Kobayashi Gunma University, JAPAN

# **Objective**

Development of simple reference current source insensitive to power supply voltage variation

# Our Approach

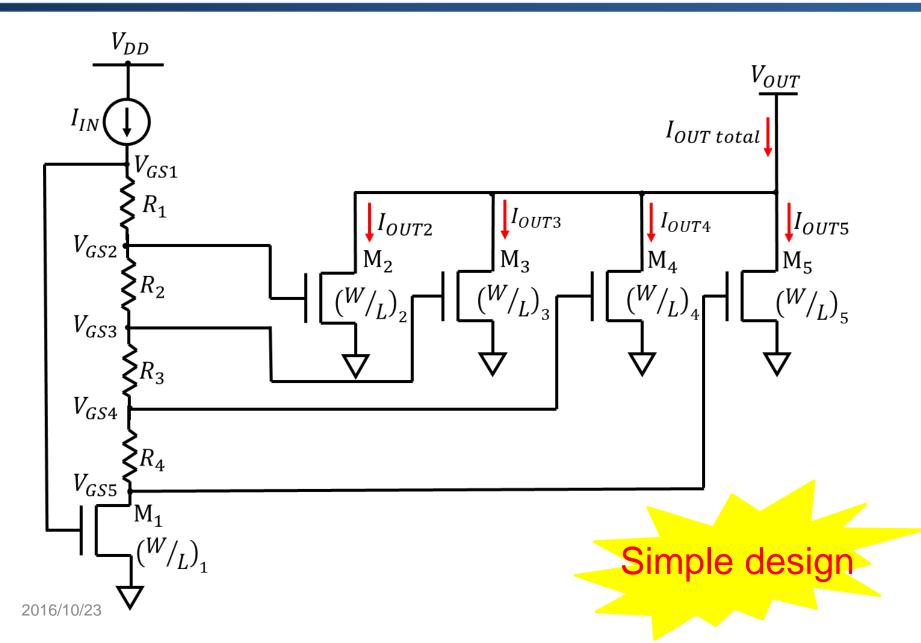

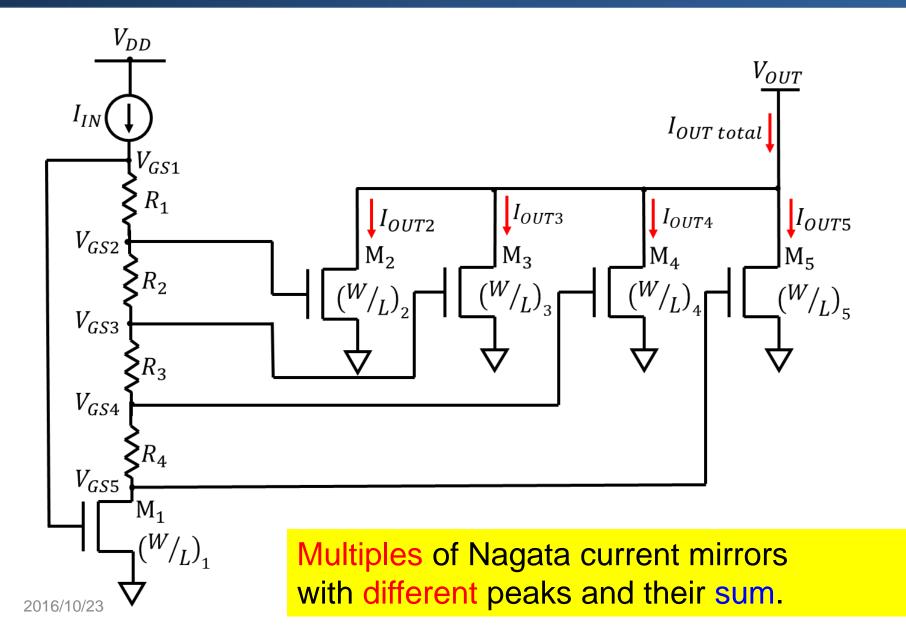

- Peaking current source invented by Dr. Minoru Nagata (Japanese) in 1966.

- Using multiple current peaks and their sum.

#### Research Background

- Nagata Current Mirror Circuit

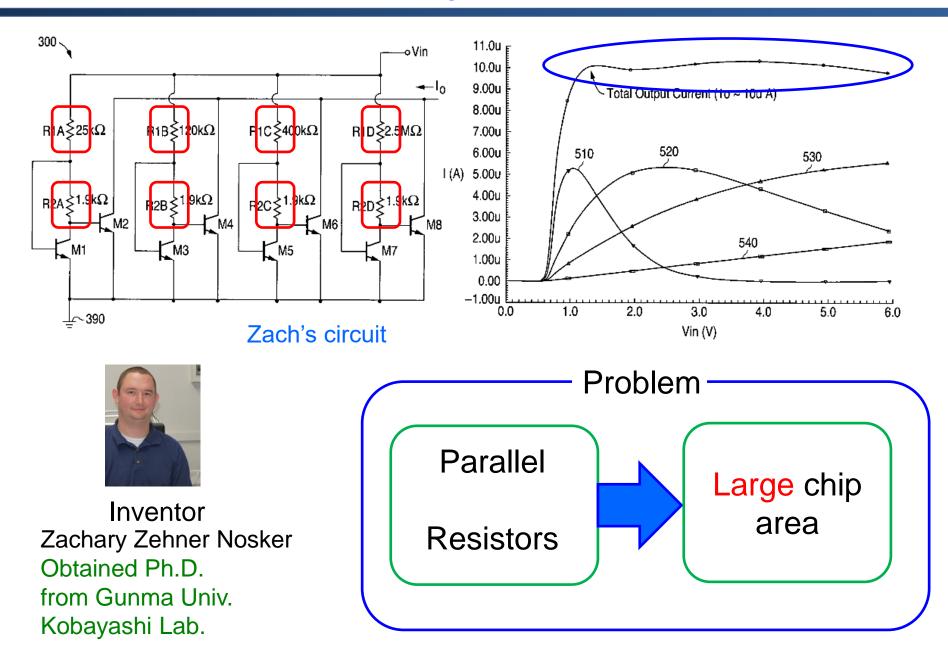

- Improved circuit (Zach's Circuit)

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

#### Research Background

- Nagata Current Mirror Circuit

- the second content with the second content of the second cont

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

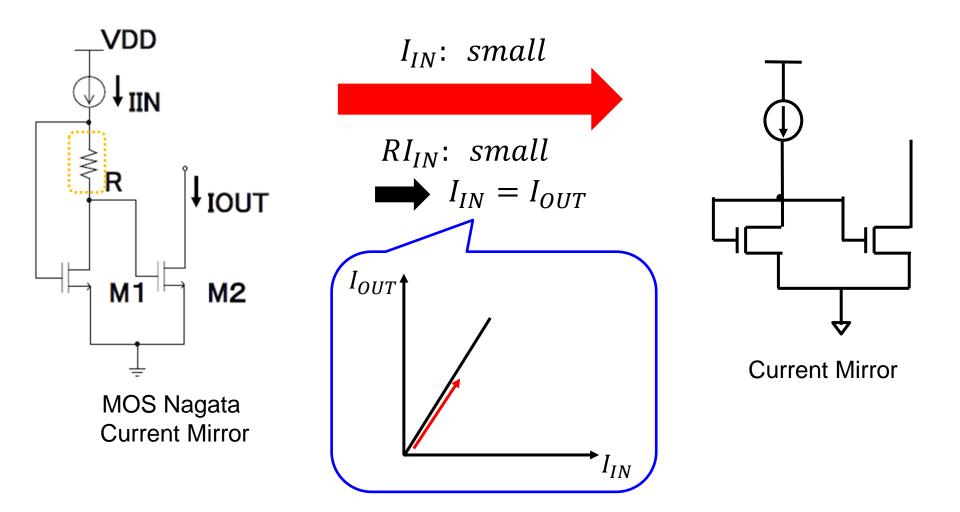

### **Research Background**

Bandgap reference circuit

- ✓ Complicated

- Large chip area.

Nagata current mirror

- Simple

- Only effective for voltage variation

#### Research Background

#### Nagata Current Mirror Circuit

- Improved circuit (Zach's Circuit)

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

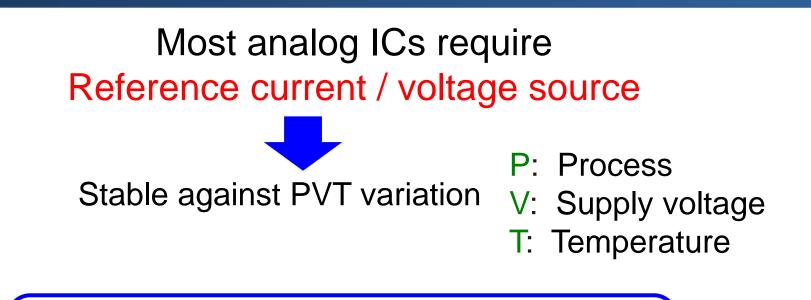

# **Original Nagata Current Mirror**

Simple Widely used. Ex: in DC-DC converter ICs

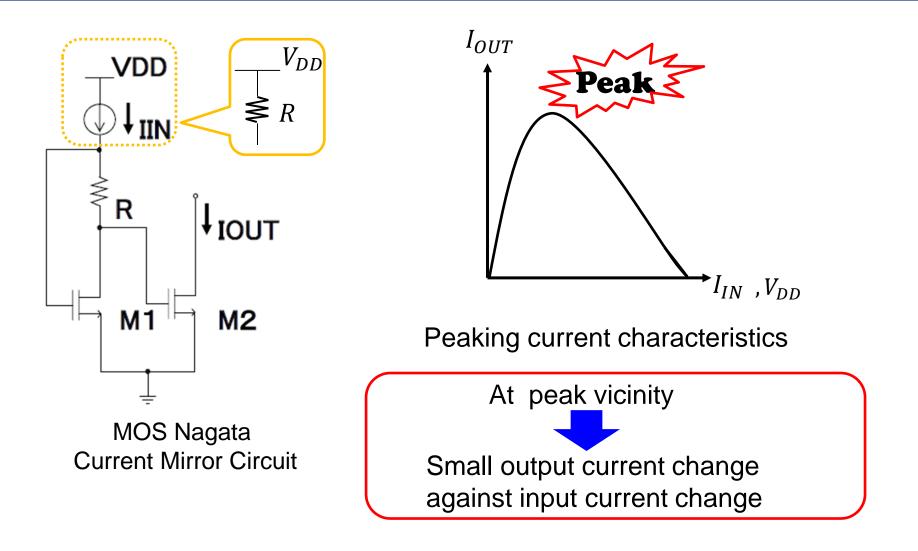

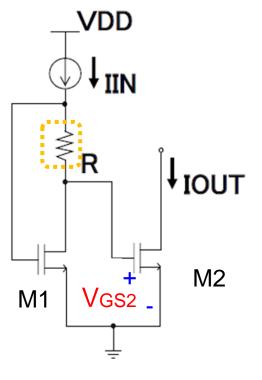

# Circuit Configuration and Operation(1)

# Circuit Configuration and Operation(2)

MOS Nagata Current Mirror Circuit

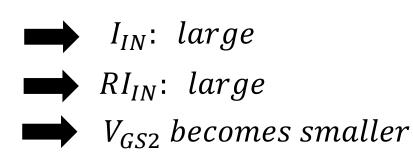

### **Inv-Iout Characteristics**

#### Research Background

- Nagata Current Mirror Circuit

- Improved circuit (Zach's Circuit)

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

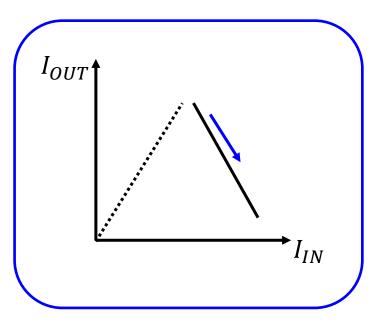

## **Previous Improved Circuit**

#### Research Background

- Nagata Current Mirror Circuit

- the second control of the second contro

#### Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

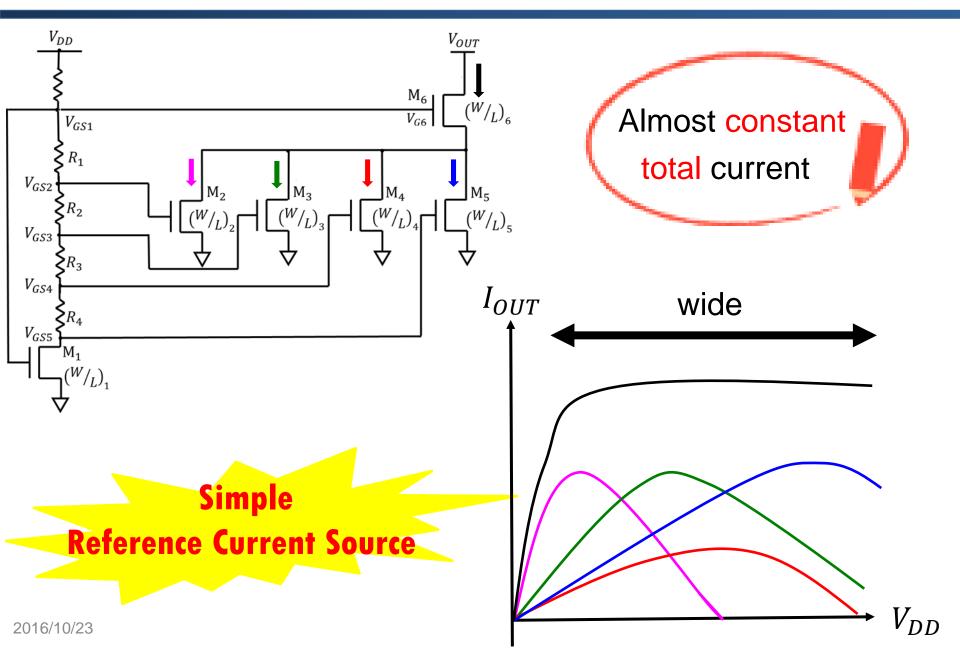

### Proposed MOS Reference Current Source

### Proposed MOS Reference Current Source

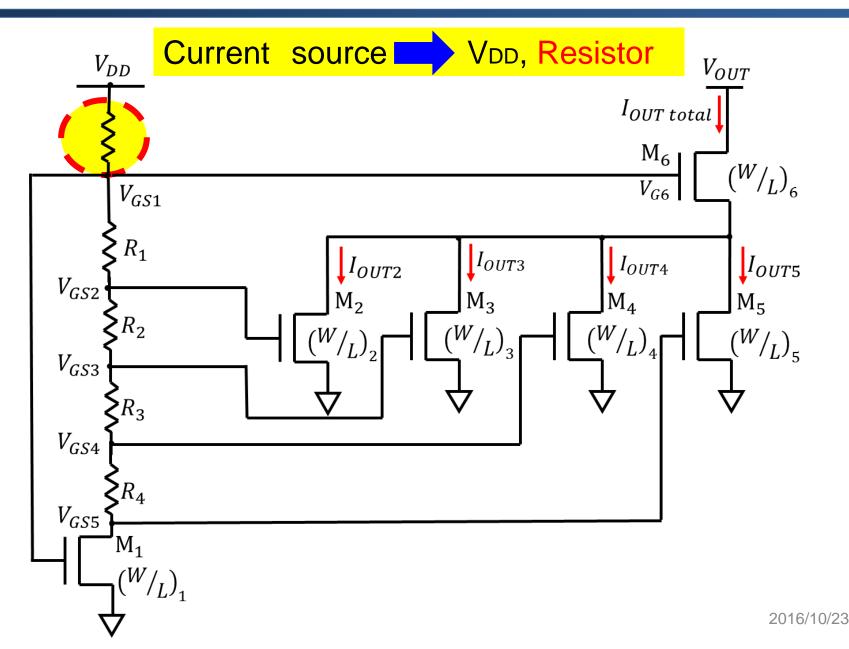

### MOS Reference Current Source Details

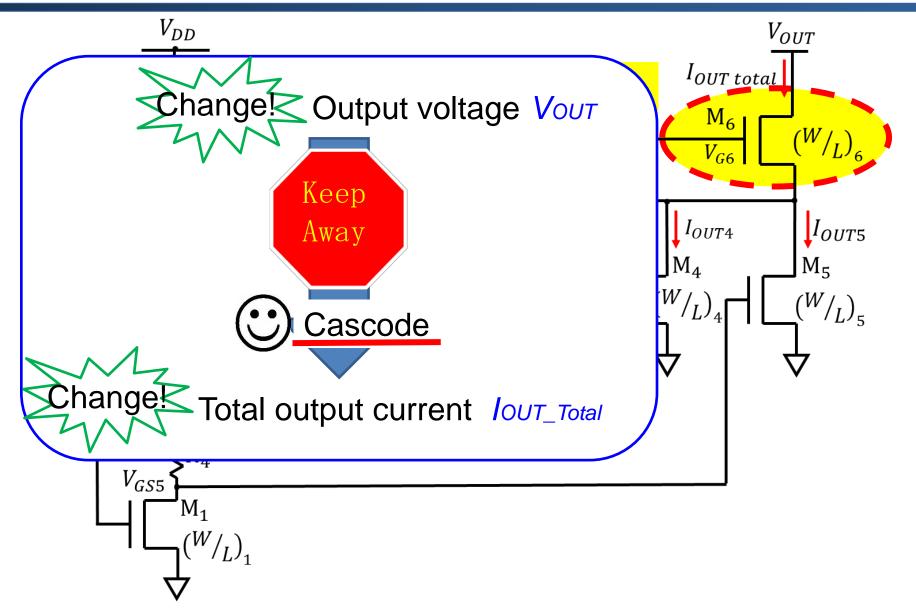

# **Cascode Configuration**

### **MOS Reference Current Source Operation**

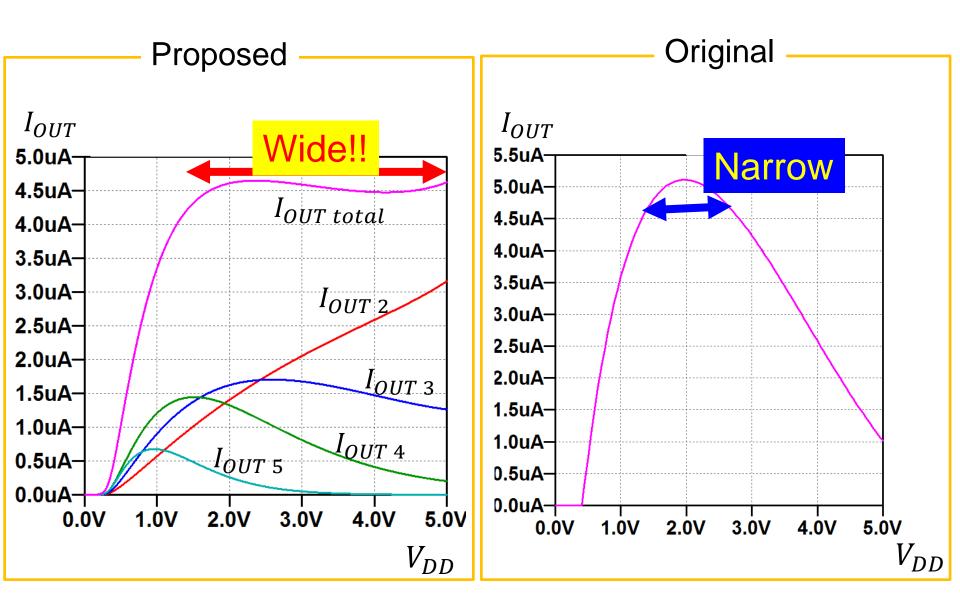

### Advantage of Proposed Circuit

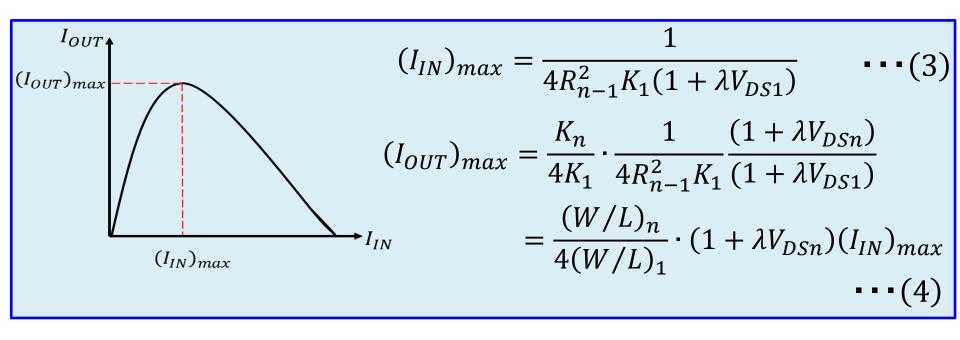

## **Analysis of Proposed Circuit**

#### Research Background

- Nagata Current Mirror Circuit

- Improved circuit (Zach's Circuit)

#### Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

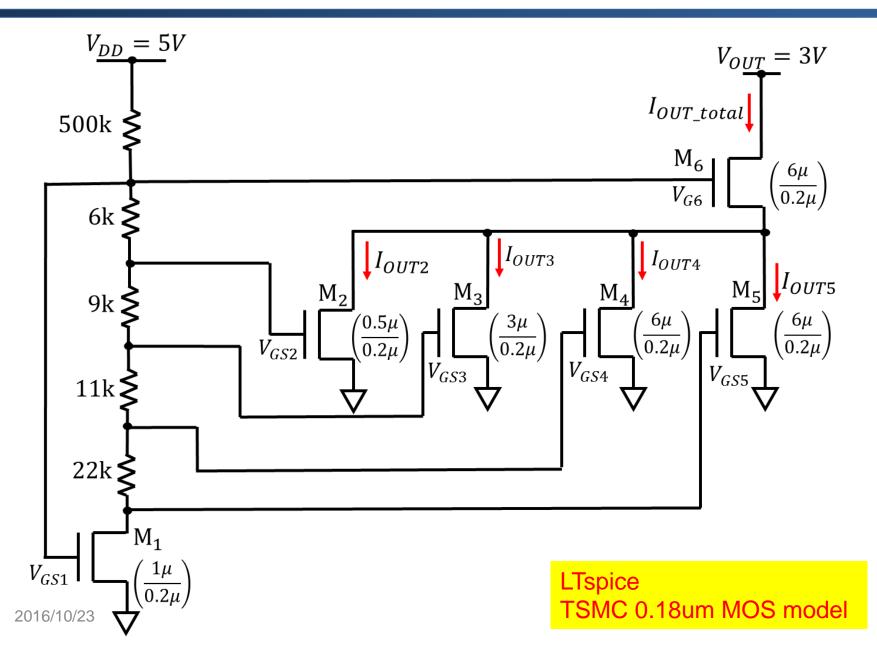

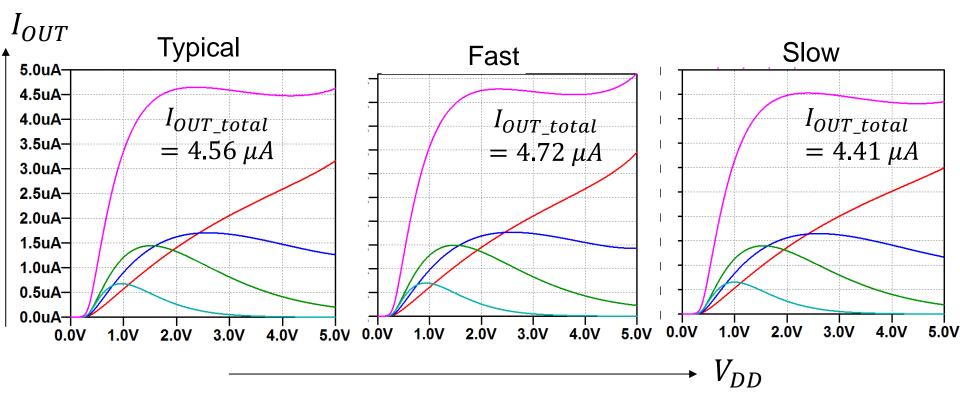

### **SPICE Simulation Circuit**

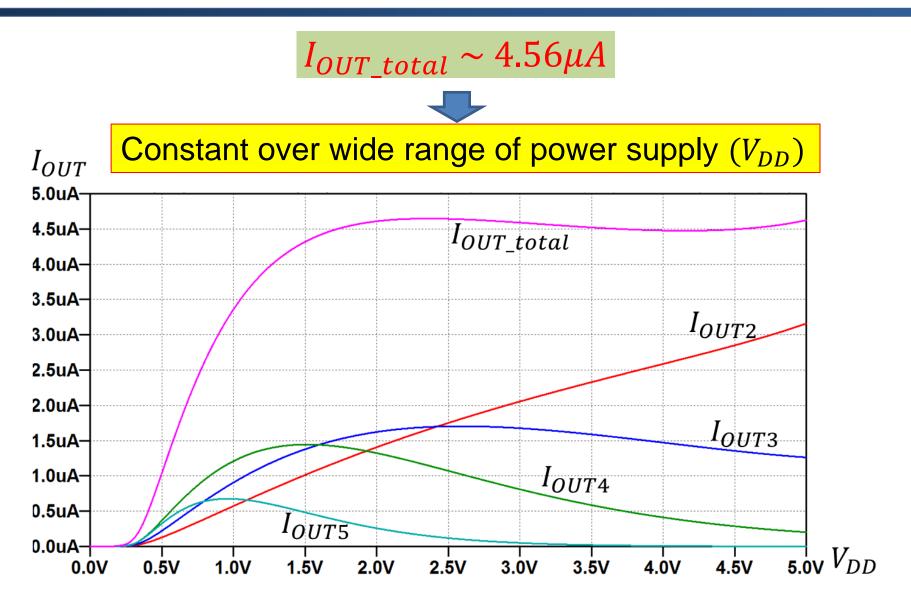

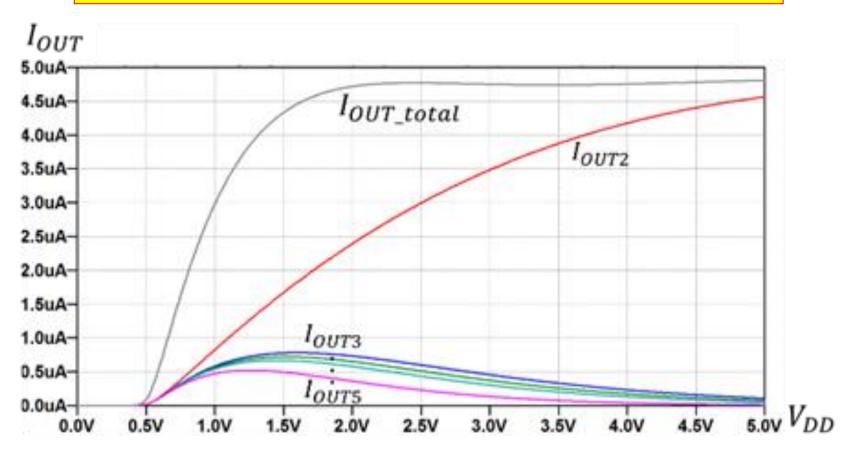

# **SPICE Simulated Characteristics**

2016/10/23

#### Research Background

- Nagata Current Mirror Circuit

- Improved circuit (Zach's Circuit)

#### Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

#### Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

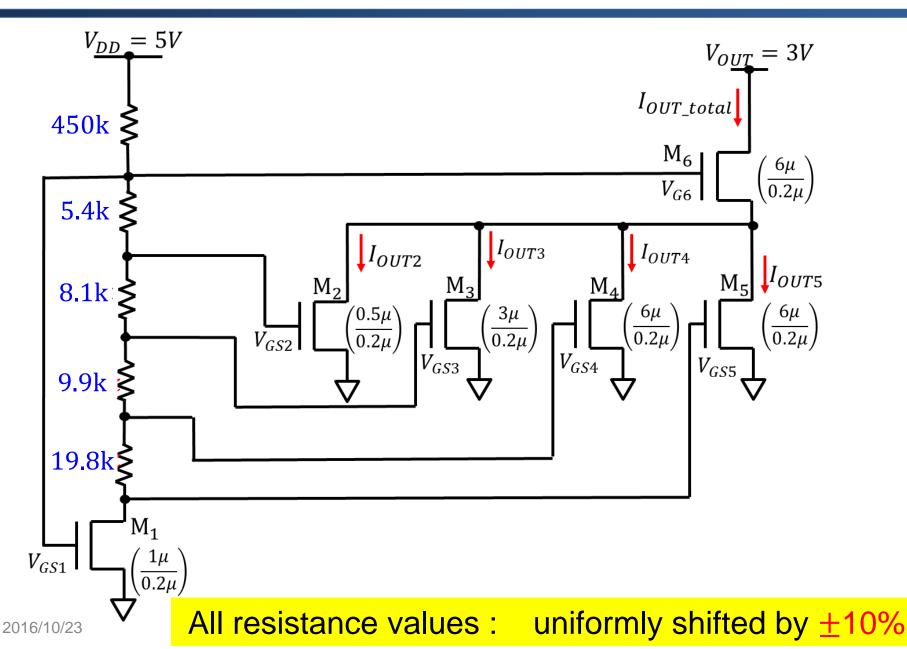

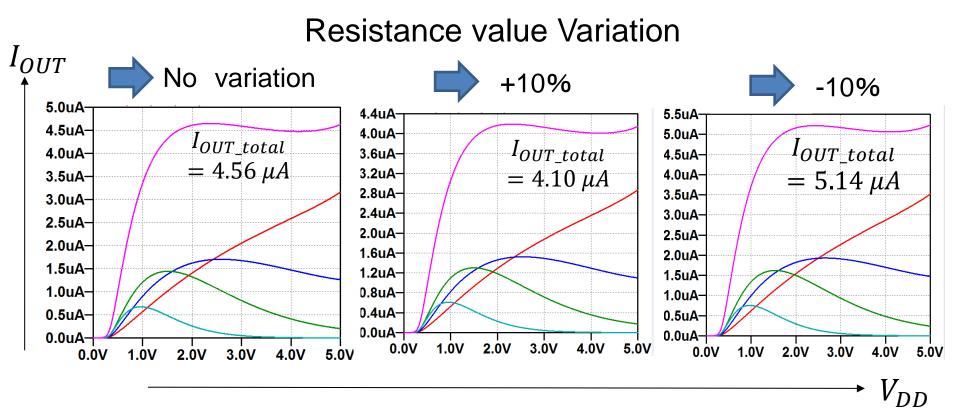

### **Influence of Resistor Variation**

## **Simulation Result**

| Resistance value Variation [%]          | +10 | -10 |

|-----------------------------------------|-----|-----|

| Total output current<br>change rate [%] | 2.4 | 1.6 |

2016/10/23

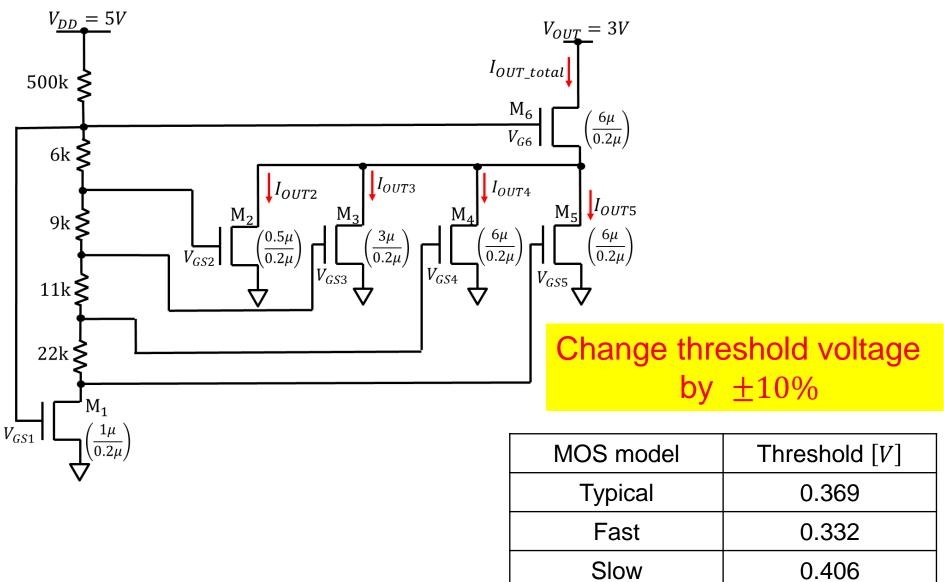

## **MOS Fast and Slow Models**

# Simulation Results with Fast & Slow Models<sup>28/38</sup>

| MOS model                               | Fast | Slow |

|-----------------------------------------|------|------|

| Total output current<br>change rate [%] | 4.4  | 2.5  |

2016/10/23

#### Research Background

- Nagata Current Mirror Circuit

- the second content (logical content) the second content (logical content content

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

- Temperature Effect

- Conclusion

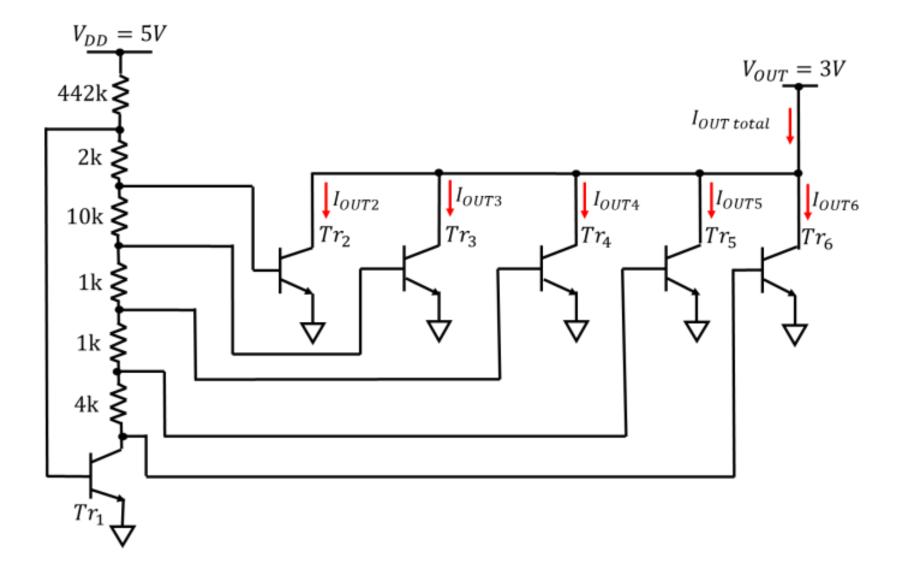

# Proposed Bipolar Reference Current Source 30/38

### **Simulation Result**

Constant over wide range of power supply  $(V_{DD})$

32/38

#### Research Background

- Nagata Current Mirror Circuit

- the second control of the second contro

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

# Temperature Effect

Conclusion

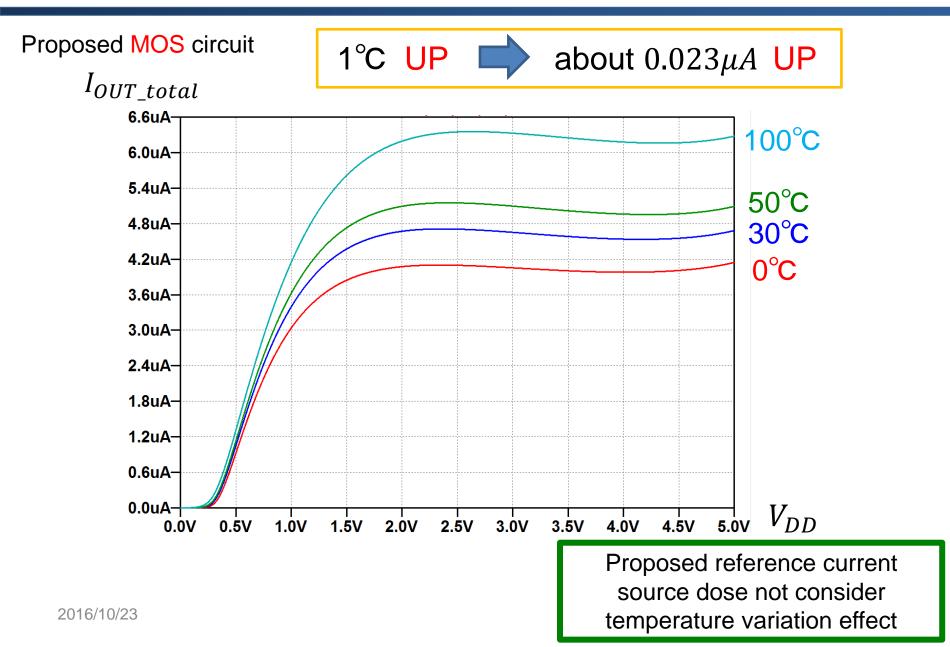

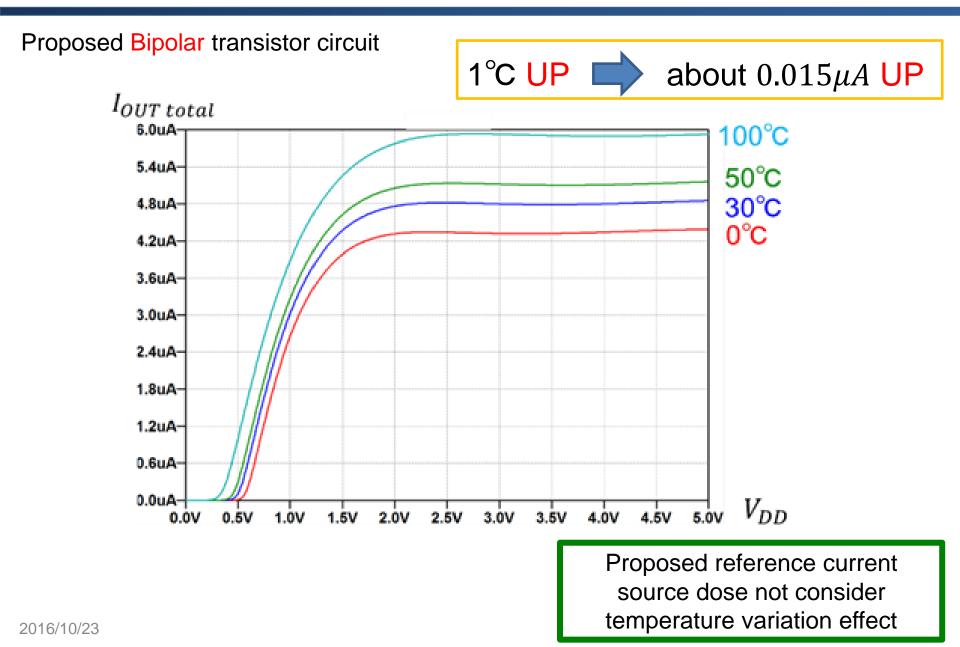

## **Temperature Effect (1)**

### **Temperature Effect**

#### Research Background

- Nagata Current Mirror Circuit

- the second content (logical content) the second content (logical content content

- Proposed MOS Reference Current Source

- Circuit Configuration and Operation

- SPICE Simulated Characteristics

- Component Variation Effects

- Proposed Bipolar Reference Current Source

Temperature Effect

### 🐡 Conclusion

### Conclusion

#### Proposal of MOS & Biploar reference current sources

Sum of multiple peaking currents

#### Comparison

| Circuit                              | Circuit<br>Simplicity | Chip<br>Area | Insensitivity<br>to VDD |

|--------------------------------------|-----------------------|--------------|-------------------------|

| Nagata Current Mirror                | $\bigcirc$            | $\bigcirc$   | $\bigtriangleup$        |

| Zach's Circuit                       | $\bigtriangleup$      | ×            | $\bigcirc$              |

| BandGap Reference                    | ×                     | 0            | $\bigtriangleup$        |

| Proposed Reference<br>Current Source | 0                     | $\bigcirc$   | $\bigcirc$              |

Design guidelines of R, W/L values are now ready for reporting elsewhere.

### Analog circuit is art & craft